Создание эффективных ускорителей нейронных сетей на базе программируемых логических интегральных схем (ПЛИС) задает новые требования к компиляторам, работающим с ПЛИС. Ускорители нейронных сетей состоят из очень большого числа идентичных схем. Примером таких схем являются умножители малой точности. Именно поэтому, для того чтобы получить максимальную производительность необходимо строить эти небольшие схемы оптимальным образом. В данном случае оптимальность подразумевается с точки зрения размера синтезируемой схемы и ее задержки. Точный синтез, основанный на задаче ВЫПОЛНИМОСТЬ (англ. satisfiability, SAT) - известная и эффективная техника для построения оптимальных схем для функций алгебры логики с маленьким числом входов. В данной работе был применен метод точного синтеза к адаптивным логическим модулям (АЛМ) современных ПЛИС корпорации Intel. Для этого был разработан программный комплекс на базе SAT-решателя, который строит оптимальные схемы на основе АЛМ блоков архитектуры Stratix10 и Agilex. Применяя данный программный комплекс для синтеза оптимальных схем умножителей небольшой размерности, было показано, что новые схемы на 10-50% эффективнее с точки зрения размера по сравнению со схемами построенными Quartus Complier. Кроме того, в некоторых случаях удалось получить схемы, которые имеют меньшее значение задержки. В заключение отметим, что, насколько нам известно, в данной работе впервые методы точного синтеза были применены к архитектурам современных коммерческих ПЛИС.

Идентификаторы и классификаторы

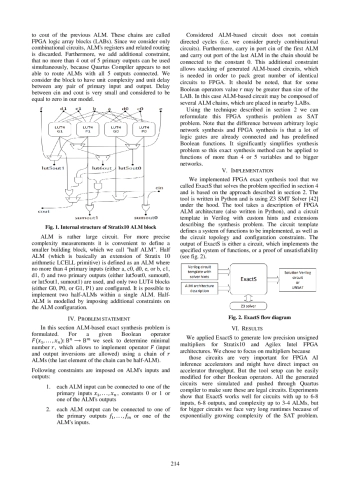

In the recent years there is a growing interest to use FPGAs for AI inference. For example, Microsoft has used FPGA to build their Brainwave AI service [1]-[2]. The key calculation that the Brainwave-like inference engines use FPGAs for is low-precision multiplication. Therefore, it is important to be able to implement low-precision multipliers in FPGA in the most optimal way.

Quartus compiler significantly improved quality of multiplier synthesis with the recent introduction of Fractal synthesis [3].

Список литературы

1. Fowers J. et al. A configurable cloud-scale DNN processor for real-time AI // 2018 ACM/IEEE 45th Annual International Symposium on Computer Architecture (ISCA). - IEEE, 2018. - P. 1-14.

2. Chung E. et al. Serving dnns in real time at datacenter scale with project brainwave // IEEE Micro. - 2018. - V. 38. -№. 2. - P. 8-20.

3. Langhammer M., Baeckler G., Gribok S. Fractal synthesis: Invited tutorial // Proceedings of the 2019 ACM/SIGDA International Symposium on Field-Programmable Gate Arrays. - 2019. - P. 202-211.

4. Kojevnikov A., Kulikov A. S., Yaroslavtsev G. Finding efficient circuits using SAT-solvers // International Conference on Theory and Applications of Satisfiability Testing. - Springer, Berlin, Heidelberg, 2009. - P. 32-44.

5. Knuth D. E. The art of computer programming, Volume 4, Fascicle 6: Satisfiability. - Addison-Wesley Professional, 2015.

6. Soeken M. et al. Practical exact synthesis // 2018 Design, Automation & Test in Europe Conference & Exhibition (DATE). - IEEE, 2018. - P. 309-314. EDN: VIAHAS

7. ExactS FPGA Exact synthesis tool. [Online]. Available: https://mks2.cs.msu.ru/root/intel\\_altera.

8. Ernst E. A. Optimal combinational multi-level logic synthesis. - University of Michigan, 2009.

9. Karp R. M. et al. A computer program for the synthesis of combinational switching circuits // 2nd Annual Symposium on Switching Circuit Theory and Logical Design (SWCT 1961). - IEEE, 1961. - P. 182-194.

10. Roth J. P., Karp R. M. Minimization over Boolean graphs // IBM journal of Research and Development. - 1962. - V. 6. - №. 2. - P. 227-238.

11. Schneider P. R., Dietmeyer D. L. An algorithm for synthesis of multiple-output combinational logic // IEEE Transactions on Computers. - 1968. - V. 100. - №. 2. - P. 117-128.

12. Lawler E. L. An approach to multilevel Boolean minimization // Journal of the ACM (JACM). - 1964. - V. 11. - №. 3. - P. 283-295.

13. Smith R. A. Minimal three-variable NOR and NAND logic circuits // IEEE Transactions on Electronic Computers. -1965. - №. 1. - P. 79-81.

14. Drechsler R., Gunther W. Exact circuit synthesis // In Int’l Workshop on Logic Synth. - 1998.

15. Knuth D. E. The art of computer programming, volume 4A: combinatorial algorithms, part 1. - Pearson Education India, 2011.

16. Hellerman L. A catalog of three-variable or-invert and and-invert logical circuits // IEEE Transactions on Electronic Computers. - 1963. - №. 3. - P. 198-223.

17. Muroga S., Ibaraki T. Design of optimal switching networks by integer programming // IEEE Transactions on Computers. - 1972. - V. 100. - №. 6. - P. 573-582.

18. Een N. Practical SAT-a tutorial on applied satisfiability solving // Slides of invited talk at FMCaD. - 2007.

19. Baugh C. R., Ibaraki T., Muroga S. Results in Using Gomory’s All-Integer Integer Algorithm to Design Optimum Logic Networks // Operations Research. - 1971. - V. 19. - №. 4. - P. 1090-1096.

20. Baugh C. R. et al. Optimal networks of NOR-OR gates for functions of three variables // IEEE Transactions on Computers. - 1972. - V. 100. - №. 2. - P. 153-160.

21. Lai H. C. et al. Minimization of logic networks under a generalized cost function // IEEE Transactions on Computers. - 1976. - V. 100. - №. 9. - P. 893-907.

22. Davidson E. S. An algorithm for NAND decomposition under network constraints // IEEE Transactions on Computers. - 1969. - V. 100. - №. 12. - P. 1098-1109.

23. Culliney J. N. et al. Results of the synthesis of optimal networks of AND and OR gates for four-variable switching functions // IEEE Transactions on Computers. - 1979. - V. 28. - №. 01. - P. 76-85.

24. Testa E. et al. Exact synthesis for logic synthesis applications with complex constraints // Proceedings of the 26th International Workshop on Logic & Synthesis (IWLS). - 2017. - №. CONF.

25. Haaswijk W. et al. Classifying functions with exact synthesis // 2017 IEEE 47th International Symposium on Multiple-Valued Logic (ISMVL). - IEEE, 2017. - P. 272277. EDN: YFMDOO

26. Soeken M. et al. Exact synthesis of majority-inverter graphs and its applications // IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems. - 2017. - V. 36. - №. 11. - P. 1842-1855. EDN: YHPADH

27. Haaswijk W. et al. A novel basis for logic rewriting // 2017 22nd Asia and South Pacific Design Automation Conference (ASP-DAC). - Ieee, 2017. - P. 151-156.

28. Haaswijk W. et al. SAT based exact synthesis using DAG topology families // 2018 55Th Acm/Esda/Ieee Design Automation Conference (Dac). - IEEE, 2018. - P. 1-6. EDN: YIJAEX

29. Chu Z. et al. Exact synthesis of boolean functions in majority-of-five forms // 2019 IEEE International Symposium on Circuits and Systems (ISCAS). - IEEE, 2019. - P. 1-5. EDN: UNJECK

30. Ложкин С.А., Зизов В.С., Шуплецов М.С., Жуков В.В., Хзмалян Д.Э., Белянков О.О. О сложности инверсных графов, реализующих булевы функции от малого числа переменных // Проблемы разработки перспективных микро- и наноэлектронных систем (МЭС). 2020. Выпуск 4. С. 95-102. DOI: 10.31114/2078-7707-2020-4-95-102 EDN: NQLJML

31. Riener H. et al. Exact synthesis of ESOP forms // Advanced boolean techniques. - Springer, Cham, 2020. - P. 177-194.

32. Stoffelen K. Optimizing s-box implementations for several criteria using SAT solvers // International Conference on Fast Software Encryption. - Springer, Berlin, Heidelberg, 2016. - P. 140-160.

33. Huang Z. et al. Fast Boolean matching based on NPN classification // 2013 International Conference on Field-Programmable Technology (FPT). - IEEE, 2013. - P. 310313.

34. Kulikov A. S. Improving circuit size upper bounds using sat-solvers // 2018 Design, Automation & Test in Europe Conference & Exhibition (DATE). - IEEE, 2018. - P. 305308. EDN: VBQEZM

35. Amaru L. et al. Enabling exact delay synthesis // 2017 IEEE/ACM International Conference on Computer-Aided Design (ICCAD). - IEEE, 2017. - P. 352-359.

36. Soeken M., De Micheli G., Mishchenko A. Busy man’s synthesis: Combinational delay optimization with SAT // Design, Automation & Test in Europe Conference & Exhibition (DATE), 2017. - Ieee, 2017. - P. 830-835. EDN: YFDUAB

37. Brayton R., Mishchenko A. ABC: An academic industrial-strength verification tool // International Conference on Computer Aided Verification. - Springer, Berlin, Heidelberg, 2010. - P. 24-40.

38. M. Soeken, The CirKit toolkit. [Online]. Available: https://github.com/msoeken/cirkit.

39. W. Haaswijk, The percy exact synthesis library. [Online]. Available: https://github.com/whaaswijk/percy.

40. Ложкин С.А., Шуплецов М.С., Коноводов В.А., Данилов Б.Р., Жуков В.В., Багров Н.Ю. Распределенная система и алгоритмы поиска минимальных и близких к ним контактных схем для булевых функций от малого числа переменных // Проблемы разработки перспективных микро- и наноэлектронных систем (МЭС). 2016. № 1. С. 40-47. EDN: WQSEEP

41. Intel Stratix 10 logic array blocks and adaptive logic modules user guide. [Online]. Available: https://www.mtel.com/content/dam/www/programmable/us/en/pdfs/literature/hb/stratix-10/ug-s10-lab.pdf.

42. The Z3 Theorem Prover. [Online]. Available: https://github.com/Z3Prover/z3.

Выпуск

Другие статьи выпуска

Методами атомно-силовой микроскопии изучена поверхность образцов аморфной электротехнической стали (фольги) Fe(Ni, Cu)(SiB) толщиной около 100 мкм, шириной 10 мм, длиной 50 мм, которая была получена методом сверхбыстрого охлаждения при распылении расплава на вращающемся барабане. На контактной поверхности фольги обнаружены характерные структурные элементы, наличие которых в различных местах поверхности может существенно влиять на электротехнические свойства материала.

В работе приводится обобщенная методика расчета схемы пассивного смесителя частот с управлением по току на любой промежуточной частоте с учетом резонансного характера входного импеданса источника тока и выходной нагрузки. Схема смесителя моделируется в среде Micro-Cap и результат сравнивается с расчетом. Предложена цепь компенсации гармоник на выходе плеч. Эта цепь позволяет существенно подавить уровень гармоник и повысить передаточный импеданс смесителя. Рассмотрены частотные зависимости передаточного импеданса.

Статья является развитием работ, в которых рассмотрена методика анализа диодных преобразователей частоты в базисе узловых потенциалов. В данной статье вводится в рассмотрение эквивалентная схема диода с учётом его емкостных параметров. Проведён линейный анализ диодных преобразователей частоты: балансного, двойного балансного и тройного балансного. Получены выражения для коэффициента передачи, развязки «вход-выход» и развязки «гетеродин-выход». Рассмотрено влияние технологического разброса параметров диодов на коэффициент передачи и развязки по портам. Проведена оценка частотных свойств преобразователей частоты. Представлены результаты расчёта и моделирования вышеперечисленных характеристик.

Усилитель мощности (УМ) класса Е широко используется в системах индуктивной передачи энергии (ИПЭ) для питания различных электронных устройств. Однако при обеспечении требуемых выходных характеристик систем возникают трудности в проектировании УМ, что ведёт к увеличению времени его разработки. Для оптимизации проектирования было выполнено сравнение выходных характеристик систем ИПЭ с УМ класса Е и систем ИПЭ с резонансным LC-контуром в передатчике. Сравнение проводилось в ходе численного моделирования систем в программах LTSpice и Matlab. В ходе исследования УМ класса Е работал в номинальном режиме как при одном коэффициенте связи катушек индуктивности систем ИПЭ, так и на заданном диапазоне этих коэффициентов. Иначе говоря, проводилась как статическая, так и динамическая регулировка конденсаторов УМ. В результате исследования отмечена сходимость выходных характеристик между системами ИПЭ с динамически регулируемым УМ класса Е и системами ИПЭ с резонансным LC-контуром в передатчике. На основе результатов исследования предложены правила проектирования УМ класса Е в зависимости от степени связи передающей и принимающей катушек индуктивности системы ИПЭ.

В статье рассмотрена математическая модель интервального измерения траекторной скорости доплеровским радиолокационным устройством. Проведен ее анализ и определены основные параметры и характеристики, влияющие на точность. Выявлена зависимость относительных ошибок при различных наклонных дальностях измерения. Построена аддитивная математическая модель относительной ошибки измерения траекторной скорости. Проверена корректность модели на экспериментальных данных. Для получения доплеровского сдвига частоты предложено радиолокационное устройство ближнего действия с двойным преобразованием частоты, которое обладает повышенной чувствительностью по сравнению с устройством с прямым преобразованием.

В сфере микро- и наноэлектроники многие ученые год за годом проявляют огромный интерес в поисках и исследованиях новых материалов, способствующих кардинальному расширению электронной компонентной базы, что связано, в первую очередь, со значительным ростом затрат производства при масштабировании научно-технических процессов [1]. Ярким примером таких материалов служат пористые оксидные пленки, актуальность исследования которых обусловлена их применением в фотодетекторах, светодиодах, катодах вакуумной микроэлектроники, в роли межслойной изоляции интегральных микросхем (ИМС) [2], наномембранах, антибликовых покрытий в приборах оптической электроники [3]. За счет применения этих пленок в качестве изолирующих материалов заметно повышается скорость распространения электрических сигналов, из-за более низкой диэлектрической проницаемости, чем у непористых структур, снижаются потери на электропроводность [4], что также позволяет использовать диоксид кремния, модифицированный углеродом, для уменьшения потери мощности в ИМС СВЧ-диапазона [5]. Целью данной статьи являлось исследование электрофизических свойств пористых пленок диоксида кремния. Объект исследования -тонкопленочная структура металл-диэлектрик-металл (МДМ) на основе диоксида кремния, модифицированного углеродом.

Рассматриваются базовые схемотехнические решения операционных усилителей (ОУ), ориентированные на изготовление на одном GaAs кристалле полевых транзисторов (field effect transistor, FET) со встроенным каналом n-типа и p-n-p транзисторов. Предлагается перспективная архитектура трехкаскадного ОУ на основе pHEMT (pseudo morphic high electron mobility transistor) и p-n-p HBT (hetero junction bipolar transistor), в которой реализуются малые значения систематической составляющей напряжения смещения нуля, обусловленной влиянием токов базы p-n-p транзисторов и его температурными и радиационными изменениями. Исследуется три варианта построения входных каскадов, в которых предусмотрено увеличение на 1-2 порядка крутизны усиления при работе pHEMT в микроамперных диапазонах токов (10-100 мкА).

Использование в оптических сетях технологий OFDM и MIMO позволили существенно увеличить скорости передачи данных в транспортных сетях использующих, методы оптического мультиплексирования. Более того, дальнейший прогресс в повышении пропускной способности одномодового оптоволокна связывают с усовершенствованием методов коммутации цифровых потоков на основе технологий WDM-SDM. Для реализации таких технологий потребуется новая электронно-компонентная база, реализуемая в виде специализированных микросхем, изготовляемых на КМОП транзисторах с субмикронными проектными нормами. В наших исследованиях мы будем использовать модели транзисторов с проектными нормами 65 нм.

Исследована структура слоев пористого кремния, сформированных при различных плотностях тока и продолжительностях анодной электрохимической обработки. Произведен статистический анализ распределения по размерам (диаметрам пор и толщине скелета) элементов матрицы пористого кремния, полученного в различных режимах анодирования. Разработана методика удаления приповерхностного слоя пористого кремния, вызывающего трудности при электрохимическом заполнении каналов пор металлами, и оценен эффект данной операции на структурные параметры внутренних областей пористого кремния. Даны рекомендации касательно применения слоев пористого кремния в составе гетероэпитаксиальных структур и нанокомпозитов на основе пористого кремния и германия, позволяющих обеспечить возможность реализации более оптимальных подходов к синтезу высокоэффективных термоэлектрических устройств.

Изложены возможности нового прибора разработки Компании ООО «НТ-МДТ» - сканирующего зондового микроскопа «ВЕГА», способного работать с образцами размером до 200х200х40 мм с предельным для атомно-силовой микроскопии разрешением для исследования свойств и метрологического контроля поверхностных наноструктур микро и наноэлектроники.

В статье предложен вариант реализации КИХ-фильтров для многостадийной архитектуры сигма-дельта АЦП с использованием перекодировочных таблиц. Приведены примеры разбиения подобного фильтра на подтаблицы и показан минимальный по площади вариант.

Теоретически исследуется поглощение света квантовой проволокой с переходом носителей из валентной зоны в донорные состояния в присутствие поперечного электрического поля. Примесный центр моделируется потенциалом нулевого радиуса. Получены выражения для коэффициента поглощения света с учётом процессов рассеяния носителей. Анализируются частотные зависимости коэффициента поглощения света при различных значениях напряженности электрического поля и при различных значениях энергии связанного состояния. Показана возможность управления положением максимума поглощения света с помощью электрического поля.

При создании высокопроизводительных вычислительных систем много усилий уделяется вопросам надежности. Децентрализованная архитектура параллельной потоковой вычислительной системы и распределение ресурсов, поддержанное на уровне аппаратуры, позволяют без дополнительных аппаратных затрат реализовать т. н. метод программного мажорирования. В статье рассматриваются варианты реализации функционала мажоритарного элемента в параллельной потоковой вычислительной системе на основе процессора сопоставлений с использованием особенностей его функционирования. Проанализированы преимущества и недостатки вариантов реализации функционала мажоритарного элемента.

Выполнен сравнительный анализ производительности отечественных и зарубежных МК с ядром Cortex-M3. Представлены оценки быстродействия и эффективности выполнения операций отечественных МК К1986ВЕ92QI, К1986ВЕ91Т и их зарубежных аналогов STM32F103C8, STM32F100RBT6. Разработаны тестовые программы для измерения быстродействия при выполнении арифметических операций с целыми числами и числами с плавающей точкой. Проведен сравнительный анализ скорости обращения к портам ввода/вывода с помощью библиотек CMSIS, SPL «Миландр» и «STMicroelectronics». Представлен программный код тестов вычисления числа п и чисел ряда Фибоначчи. Разработаны тесты и представлены результаты расчета числа из ряда Фибоначчи рекурсивным вызовом функции и линейным алгоритмом расчета в цикле.

Предлагается «базовая» структура для организации контроля вычислений на выходах комбинационных схем по классическим кодам Хэмминга с дополнительным контролем самодвойственности каждой контрольной функции. Для этого в схеме встроенного контроля применен кодер классического кода Хэмминга с от=4 информационными разрядами, позволяющий производить самодвойственное сжатие сигналов с последующим контролем вычислений. В работе приводятся некоторые результаты моделирования самодвойственных устройств, получаемых по предлагаемой структуре организации схемы встроенного контроля. Представленный способ организации схем встроенного контроля может эффективно применяться при синтезе самодвойственных устройств с большим количеством выходов с выделением групп по четыре выхода в каждой, синтезом отдельных схем встроенного контроля и их дальнейшей совместной оптимизацией для снижения показателей структурной избыточности.

В этой статье рассмотрены методы сокращения до нескольких секунд времени загрузки от подачи питания до старта инициализации операционной системы. Рассмотренные методы являются универсальными, и для реализации некоторых из них нужна аппаратная поддержка. Эти методы испытаны в вычислительных комплексах на основе процессоров Эльбрус и проанализирована их эффективность.

В данной работе описывается новый способ аппаратного преобразования чисел из системы остаточных классов в двоичную систему счисления. Предложенный для этой цели метод опорных точек основывается на использовании небольшого арифметического блока и сокращенных таблиц поиска (Look up Table (LUT)), что позволяет пользоваться быстродействием LUT и в то же время решать проблему большой площади на кристалле. Метод опорных точек сравнивается с реализацией, основанной на модифицированной Китайской теореме об остатках. Результаты свидетельствуют о том, что новый метод имеет существенный выигрыш в задержке на критическом пути, а также обладает гибкостью, позволяющей подстраивать аппаратную реализацию под нужды разработчика.

В данной работе представлены результаты параметрической оптимизации эвристическим поиском модального фильтра на двухсторонней печатной плате с лицевыми и боковыми связями. Данное устройство позволяет защитить радиоэлектронное оборудование от импульса сверхширокополосной помехи. Оптимизация выполнялась по трем основным критериям: амплитудному, диапазонно-временному и интервальновременному. Для оптимизированных параметров представлены результаты ослабления при изменении граничных условий на концах пассивных проводников на короткое замыкание (КЗ) - холостой ход (ХХ) и ХХ-КЗ. Показано, что при изменении граничных условий ослабление оценивается амплитудой дополнительных импульсов, а не импульсов мод. Достигнуто ослабление в 4 раза по отношению к половине э. д. с. при нагрузках на концах пассивных проводников по 50 Ом и 10 раз при ХХ-КЗ. Разность максимальной и минимальной погонных задержек импульсов максимизирована до 2,45 нс/м. Достигнуто выравнивание разностей погонных задержек мод 3 и 2, 7 и 6 (0,77 нс/м), а также максимизация для мод 6 и 3 (0,91 нс/м).

С использованием средств TCAD проведена оценка влияния радиационного воздействия в диапазоне доз 20кРад - 1000кРад и толщины подзатворного окисла на сдвиг порогового напряжения и чувствительность пМОП-дозиметра на базе КМОП-технологии с изоляцией LOCOS, в котором роль подзатворного окисла выполняет толстый изолирующий слой (FOXFET). Модель FOXFET сформирована в TCAD посредством моделирования КМОП-технологического маршрута с проектными нормами 0.6 мкм. Результаты моделирования показали, что чувствительность падает с ростом дозы облучения, наибольший спад наблюдается при малых дозах до 50 кРад, при дальнейшем увеличении дозы вплоть до 1000кРад наблюдается плавное снижение, которое можно объяснить постепенным насыщением ловушек в окисле зарядом. Существенный рост чувствительности прибора наблюдается с ростом толщины окисла. С помощью моделирования также рассчитаны зависимости чувствительности дозиметра от режимов формирования локального окисла.

Представлены результаты совершенствования анализа распространения импульсных сигналов в связанных линиях передачи на примере многокаскадных структур на основе витка меандровой линии (МЛ). Для этого получены условия разложения сверхкороткого импульса (СКИ) в многокаскадных МЛ с произвольным поперечным сечением и количеством каскадов. Их апробация выполнена на примере структур с лицевой связью из 2, 3 и 4 витков, показавших ослабление амплитуды СКИ 9,3, 24,1 и 84,9 раза соответственно. Кратко описан математический аппарат и функционал программного модуля для анализа отклика таких структур. Представлена демонстрация работы модуля. Результаты работы позволят упростить и ускорить анализ многокаскадных структур на основе связанных линий.

В настоящей статье рассмотрены методы учета паразитных эффектов корпуса и разварочных проволочек. Представлена методика моделирования QFN корпусов, которая может быть использована при построении табличных моделей корпусов различных размеров. Методика основана на использовании результатов трехмерного электромагнитного моделирования. Методика моделирования использована при построении табличной модели отечественного QFN корпуса, размерами 3×3 мм2. Для верификации разработанной методики используются измерения СВЧ МИС диапазона частот 2-7 ГГц до корпусирования и после. Приведено сравнение результатов моделирования и измерений СВЧ МИС в корпусе.

К современным импульсным источникам вторичного электропитания предъявляют требования по обеспечению электромагнитной совместимости. Для удовлетворения требованиям стандартов разработчики применяют специальные схемотехнические решения и входные фильтры. Чтобы правильно спроектировать фильтр разработчику нужно знать профиль кондуктивных помех, создаваемых преобразователем. В данной работе предложен подход к определению профиля кондуктивных помех на основе упрощённой модели микрополосковой линии Хаммерстада-Дженсена. Описанный в работе метод позволяет эвристически оценить паразитные параметры межсоединений на основе длин проводников между компонентами и параметров технологического стека на этапе разработки схемы. Приведены результаты сравнения профиля электромагнитных помех полученного в результате классического моделирования схемы преобразователя, моделирования по предложенному методу и профиля, полученного в результате измерений характеристик собранного макета преобразователя в лаборатории ЭМС. Предложенный метод позволил обнаружить гармонические составляющие помех в мегагерцовом диапазоне частот.

Представлены результаты анализа и оптимизации эволюционными методами витка меандровой микрополосковой линии с учетом влияния температуры окружающей среды в диапазоне от минус 50 до 150 °C. Использована простая температурная модель линейного изменения параметров витка. В результате анализа выявлено, что изменение температуры во всем диапазоне приводит к уменьшению погонных задержек четной и нечетной мод витка до 3,23 и 2,42% соответственно и уменьшению максимальной амплитуды импульсного сигнала на выходе линии до 0,17% но увеличению среднего геометрического волновых сопротивлений четной и нечетной мод линии до 3%. Продемонстрирована возможность параметрической одно- и двухкритериальной оптимизации поперечного сечения витка с учетом влияния температуры с помощью двух методов оптимизации: генетических алгоритмов и эволюционных стратегий. Выявлено хорошее согласование результатов оптимизации двумя методами, но при близких наборах оптимальных параметров время оптимизация эволюционными стратегиями оказалось в 7 раз меньше.

Снижение потребляемой мощности является одной из важнейших задач проектирования современных СБИС. Существуют различные подходы к решению данной задачи. Одним из методов, позволяющих сократить потребляемую мощность является использование библиотек многоразрядных триггеров. Наиболее длительным этапом маршрута проектирования библиотеки многоразрядных триггеров является этап характеризации. В данной статье предлагается методика, позволяющая пользователю сократить временные затраты на характеризацию многоразрядного триггера за счет незначительной потери точности.

В данной работе разбирается применение алгоритмов машинного обучения для прогнозирования мощности рассеивания энергии за счет переключений компонентов схем на начальном этапе физического проектирования интегральных схем (ИС) для конкретной архитектуры. Реалистичная оценка потребляемой мощности возможна на заключительных этапах маршрута проектирования ИС, что может создать дополнительную итеративность в маршруте для оптимизации энергопотребления. Предложенный метод позволяет довольно точно спрогнозировать конечное значение рассматриваемого вида энергопотребления с высокой точностью для различных типов стандартных ячеек при различных сценариях и конфигурациях планировки. Недостатком метода является необходимость прохождения полного маршрута проектирования выбранной схемы с выбранным диапазоном параметров для сбора данных, нужных для обучения моделей машинного обучения, что требует дополнительных машинных и временных ресурсов.

Метод моделирования цифровых микроэлектронных систем широко используется при проектировании последних. При этом важным этапом является проверка проекта на правильность функционирования цифровой системы. На компьютерную модель проекта подаются проверочные тесты, и разработчик анализирует правильность или ошибочность изменения выходных и внутренних сигналов проектируемой системы. При этом должна осуществляться проверка правильности как выполнения всех функций системы, так и всех возможных последовательностей функций. В данной работе предлагается модель и методика проверки последовательностей функций цифровой системы.

В данной работе рассматривается труднорешаемая комбинаторная задача построения топологического рисунка графа. В соответствии с предложенным в данной статье подходом решение этой задачи разбивается на несколько этапов, вводятся основные определения и ограничения предлагаемых математических моделей. Основой построения моделей служат методы дискретной оптимизации и теория вращения вершин графа. Для построения математической модели решается задача выделения плоской части графа, которая рассматривается как комбинаторная задача нахождения подмножества изометрических циклов графа. Представленный метод выделения плоской части графа основан на выделении базиса изометрических циклов графа модифицированным алгоритмом Гаусса с последующим выделением плоской части методом градиентного спуска. Рассматриваются методы построения топологического рисунка графа с минимальным числом пересечений.

В работе рассматривается алгоритм распределения соединений по слоям в задаче многослойной глобальной трассировки, базирующейся на биоинспирированных методах поиска. Решение задачи глобальной трассировки базируется на подходе, включающем две стадии. На первой стадии решается задача однослойной трассировки. На второй -выполняется «распределение соединений по слоям». Разработанные алгоритмы реализованы в виде двух программ: эвристического распределения соединений по слоям и разнесения соединений по слоям методом муравьиной колонии. Решения, полученные в процессе выполнения глобальной трассировки предложенным алгоритмом, на 2-5% лучше, в сравнении с достигнутыми результатами известных трассировщиков. Общая оценка временной сложности лежит в пределах О(n2)-О(n3).

Работа посвящена анализу перспектив использования языка визуальных языков моделирования для синтеза системного проекта ПЛИС. Проанализированы общие подходы использования визуальных языков и выявлены основные направления их применения при проектировании (синтезе) проекта ПЛИС. Показано, что применение визуальных языков позволяет ускорить и упростить процесс проектирования посредством повторного использования уже имеющихся шаблонов архитектуры.

Обратное проектирование СБИС - мощный инструмент, используемый при верификации проекта для повышения быстродействия средств моделирования аппаратуры, а также для обнаружения незаконных вложений в процессе ее производства. Задача обратного проектирования СБИС заключается в построении спецификации устройства путем анализа его аппаратной реализации в виде СБИС. Основным этапом обратного проектирования является декомпиляция плоского нетлиста транзисторной схемы, которая состоит в извлечении из него описания на уровне логических элементов. В работе предлагаются программные средства выделения логической схемы из плоского SPICE-описания транзисторной схемы. Приводятся примеры обратного инжиниринга практических примеров транзисторных схем.

Выполнен цикл моделирования электрических характеристик связанных автогенераторных схем. Обсуждаются результаты моделирования четырёх связанных мемристорных осцилляторов, для которых обеспечиваются режимы синхронизации с коллективным захватом частоты при возможном различии фаз.

Статистика статьи

Статистика просмотров за 2025 год.

Издательство

- Издательство

- ИППМ РАН

- Регион

- Россия, Москва

- Почтовый адрес

- 124365 Москва, Зеленоград, ул. Советская, дом 3

- Юр. адрес

- 123182 Россия, Москва, пл. Академика Курчатова, д. 1

- ФИО

- Гаврилов Сергей Витальевич (Директор)

- E-mail адрес

- ippm@ippm.ru

- Контактный телефон

- +7 (499) 7299890

- Сайт

- https://ippm.ru